Advancing humanity.

Engineering remarkable.

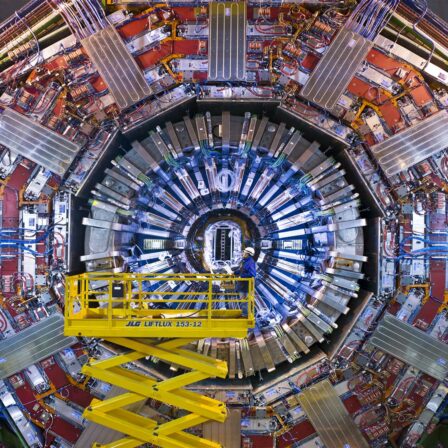

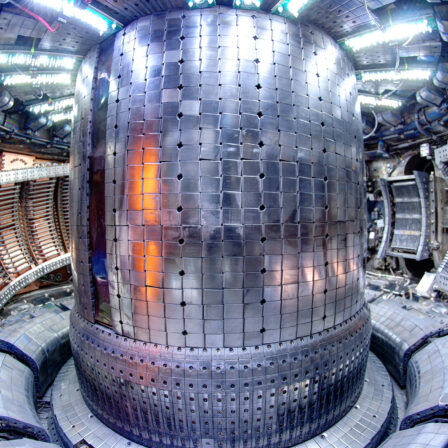

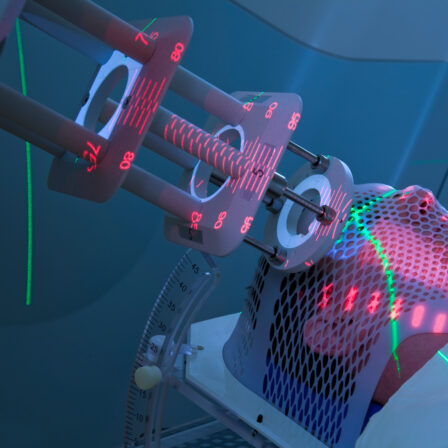

Cosylab拥有全球领先的软硬件产品和专家咨询服务,助力各大机构及组织取得科学突破和医疗创新,并积极参与核聚变工程,为世界带来清洁能源。

问题咨询

如有任何问题,欢迎垂询我们的专家团队

企业亮点

为什么与我们合作

卓越的专业知识和创新能力

涵盖科学、医疗及工业应用

一流的软件解决方案

适用于世界上最先进的系统和设备

20+年行业经验

复杂软件架构管理经验,应对各种苛刻要求

全球300+庞大团队

高技能的开发人员和工程师团队

社会责任

承诺改善社会,推动科学发现、清洁能源和癌症治疗

系统工程实践

过程经验证,保证按时预算内交付

规范流程

经ISO认证,并符合IEC标准

国际影响力

总部位于欧洲,全球遍布分支机构

灵活且可靠的伙伴

随机应变,陪伴客户走上成功之路

关于COSYLAB